## SERVER-BASED DATA PUSH ARCHITECTURE FOR DATA ACCESS PERFORMANCE OPTIMIZATION

$\mathbf{B}\mathbf{Y}$

## SURENDRA BYNA

## DEPARTMENT OF COMPUTER SCIENCE

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Department of Computer Science in the Graduate College of the Illinois Institute of Technology

Approved \_\_\_\_\_

Adviser

Chicago, Illinois December 2006 © Copyright 2006

Surendra Byna

All rights reserved

#### ACKNOWLEDGEMENT

It has been a long journey to get to this point and it would not have been possible without the cooperation, advice, help, and patience of numerous people around me. It is my pleasure to take this opportunity to thank all those who have contributed to making my professional and personal life better.

It is difficult to overstate my gratitude to my Ph.D. advisor, Professor Xian-He Sun. He has been the motivation and guiding force for me to take up this path. Without his consistent support and advice this work would not have been possible. I heartily thank Dr. Sun for giving me freedom to research, for guiding me into a right direction, and for his personal care.

I am extremely thankful to Dr. Rajeev Thakur and Dr. Bill Gropp, for encouraging me and giving me excellent ideas for research. I look forward to working with them in the future beyond this dissertation. I thank Dr. Kirk Cameron for his advice, and Dr. Hong Zhang for her encouragement.

I thank my thesis committee members Dr. Zhiling Lan, Dr. Cynthia Hood, Dr. Dietmar Rempfer, and Dr. James Stine for providing valuable feedback and suggestions. Dr. Lan has been helpful in giving guidance at group meetings of SCS Laboratory, for which I am very thankful to her.

I thank all our SCS lab members for their friendship, thoughts and suggestions in many aspects of my life. I thank Ming Wu for his help in numerous occasions. Cong Du has been a great friend through out my stay at the lab. Conversations with Nehal Mehta have always been entertaining and informative. I thank Yong Chen for his collaboration in my research work and for being a very nice friend. I also thank Yawei Li, Xiaoshan He, Petre Brotea, Kasidit, Luciano Piccoli, Gregor Tamindza, and John Sohn for their criticism in my research and friendship.

Numerous friends helped and encouraged me through out this journey. I am grateful to Sairam and Srinivas Chinnam for their support and keeping in touch with my parents often. I thank Shinta for being very caring. I appreciate Rajasekar Karawalla, Rahul Bhuman, Ravi Yeluguri, Deepthi, Prasanth Veera, Hareesh Achi, Madhavi, Vinay Kudithipudi, Sudheer Palsani, Srinivas Banda, and Hiranmayee for their support in many ways. I also thank all my other friends who helped in developing as a better human being.

Without the help of my relatives, I cannot imagine my being at this stage. Especially, I am thankful to Ravindra bava, Venu, Murali, Venkateswarlu uncle, Sujatha aunty, and Manjula akka for being there at all occasions in our family and for helping my parents from time to time. I appreciate my cousins Purnima, Anupama, Rajesh, Srikanth, Sudhir, Venkateswarlu, and Subhashini for their friendship. I take this opportunity to express my gratitude to Raghaviah uncle for his priceless advice, which I hope I could use in each step of my life, and Uma aunty for her loving support. Finally and most importantly, I cannot thank my family enough for their unconditional love. My brother-in-law, Hima Kumar and his family members have been very accepting and loving. My sister, Jyothi has been cool and cheering on for my success. My parents, Suguna and Parabrahmam Byna have been patient with me. They have been enormously supportive of me through out my life. They made sure I get quality education for my career and for my life. For all they have done to me in my growth, I dedicate this dissertation to my parents. I hope I could do more for them in the future. I thank the forces of nature and God for keeping me healthy and mentally strong.

# TABLE OF CONTENTS

| I                                          | Page |

|--------------------------------------------|------|

| ACKNOWLEDGEMENT                            | iii  |

| LIST OF TABLES                             | vii  |

| LIST OF FIGURES                            | viii |

| LIST OF SYMBOLS                            | xi   |

| ABSTRACT                                   | xii  |

| CHAPTER                                    |      |

| 1. INTRODUCTION                            | 1    |

| 1.1 DATA ACCESS PERFORMANCE                | 1    |

| 1.2 PROBLEM STATEMENT                      | 4    |

| 1.3 OUR APPROACH                           | 6    |

| 1.4 MOTIVATION                             | 8    |

| 1.5 THESIS                                 | 9    |

| 1.6 OVERVIEW OF THE DISSERTATION           | 9    |

| 2. LITERATURE REVIEW                       | 11   |

| 2.1 DATA ACCESS OPTIMIZATION               | 11   |

| 2.2 HARDWARE DATA PREFETCHING              | 13   |

| 2.3 SOFTWARE LEVEL OPTIMIZATIONS           | 15   |

| 2.4 SUMMARY                                | 21   |

| 3. SERVER-BASED DATA PUSH ARCHITECTURE     | 22   |

| 3.1 MEMORY SUBSYSTEM                       | 22   |

| 3.2 DATA PUSH SERVER ARCHITECTURE          | 27   |

| 3.3 MONITORING DATA ACCESSES               | 30   |

| 3.4 PREDICTION OF SPATIAL ACCESS PATTERNS  | 35   |

| 3.5 PREDICTION OF TEMPORAL ACCESS PATTERNS | 38   |

| 3.6 PUSHING PREDICTED DATA                 | 40   |

| 3.7 BENEFITS OF DPS                        | 45   |

| 3.8 IMPLEMENTING DPS ON CELL PROCESSOR     | 47   |

| 3.9 SUMMARY                                | 50   |

| 4. | MODELING DATA ACCESS PERFORMANCE              | 52  |

|----|-----------------------------------------------|-----|

|    | 4.1 MEMORY PERFORMANCE MODELS                 | 52  |

|    | 4.2 DATA ACCESS PATTERNS                      | 56  |

|    | 4.3 SIMPLE MEMORY ACCESS COST (SMAC) MODEL    | 58  |

|    | 4.4 MODEL VERIFICATION                        | 65  |

|    | 4.5 UTILIZATION OF SMAC MODEL                 | 73  |

|    | 4.5 UTILIZATION OF SMAC MODEL<br>4.6 SUMMARY  | 73  |

|    | 4.0 SUMMART                                   | 13  |

| 5. | DATA ACCESS OPTIMIZATION FOR MIDDLEWARE       | 76  |

|    | 5.1 MEMORY COMMUNICATION                      | 77  |

|    | 5.2 CLASSIFICATION OF PARALLEL COMMUNICATION  | 80  |

|    | 5.3 IDENTIFYING MEMORY COMMUNICATION          | 85  |

|    | 5.4 MPI DERIVED DATATYPES                     | 89  |

|    | 5.5 DATA ACCESS OPTIMIZATION FOR DATATYPES    | 93  |

|    | 5.6 PERFORMANCE EVALUATION                    | 100 |

|    | 5.7 SUMMARY                                   | 108 |

| 6. | PERFORMANCE RESULTS WITH DPS ARCHITECTURE     | 111 |

|    | 6.1 SIMPLESCALAR SIMULATOR                    | 111 |

|    | 6.2 DPS IMPLEMENTATION ON SIMPLESCALAR        | 112 |

|    | 6.3 SIMULATION ENVIRONMENT                    | 115 |

|    | 6.4 SIMULATION RESULTS                        | 118 |

|    | 6.5 SUMMARY                                   | 122 |

| 7. | APPLICATIONS OF OUR DATA ACCESS MODELS        | 124 |

|    | 7.1 MEMORY SERVERS                            | 124 |

|    | 7.2 HIGH END COMPUTING I/O                    | 140 |

|    | 7.3 ENERGY-PERFORMANCE TRADEOFF               | 150 |

|    | 7.4 SUMMARY                                   | 158 |

| 8. | CONCLUSIONS AND FUTURE WORK                   | 159 |

|    | 8.1 SUMMARY OF CONTRIBUTIONS                  | 159 |

|    | 8.2 IMPACT                                    | 162 |

|    | 8.3 FUTURE WORK: ENERGY-PERFORMANCE TRADEOFF. | 163 |

|    | 8.4 FUTURE WORK: HIGH-END COMPUTING I/O       | 164 |

|    | 8.5 SUMMARY                                   | 166 |

|    |                                               | 100 |

|    |                                               |     |

| BIBLIOGRAPHY |  | 169 |

|--------------|--|-----|

|--------------|--|-----|

# LIST OF TABLES

| Table                                                   |     |

|---------------------------------------------------------|-----|

| 3.1 Prediction strategies for data access patterns      | 35  |

| 4.1 Memory hierarchy parameters                         | 59  |

| 4.2 Data access parameters                              | 60  |

| 4.3 Number of cache misses for all data access patterns | 65  |

| 6.1 Simulator configuration                             | 113 |

| 6.2 Benchmark kernels                                   | 116 |

# LIST OF FIGURES

| Figure                                                                      | Page   |

|-----------------------------------------------------------------------------|--------|

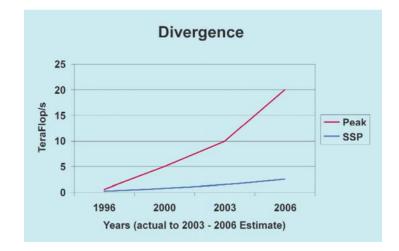

| 1.1 Growing gap between peak and sustained performance                      | 2      |

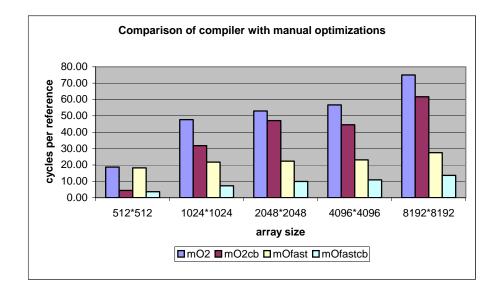

| 2.1 Comparison of compiler performance with manual optimizations            | 18     |

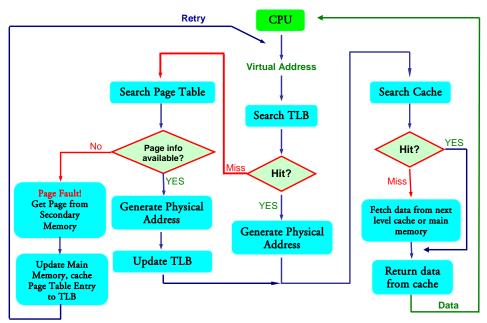

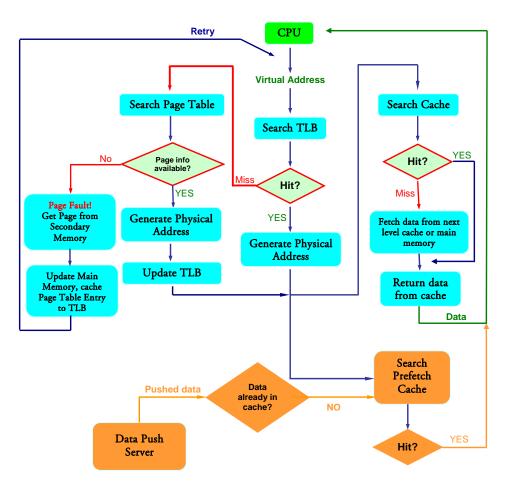

| 3.1 Processing data request by CPU                                          | 23     |

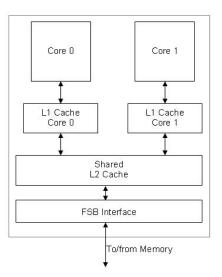

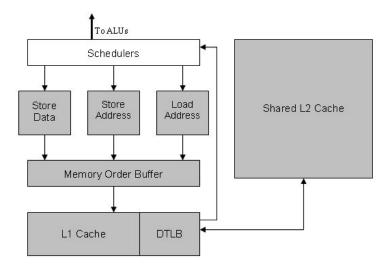

| 3.2 Multicore processor architecture (Intel Core)                           | 25     |

| 3.3 Memory subsystem of Intel Core architecture                             | 26     |

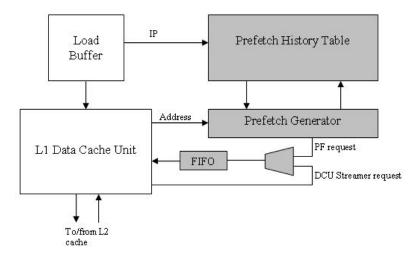

| 3.4 Instruction Pointer-based prefetcher of Intel Core architecture         | 26     |

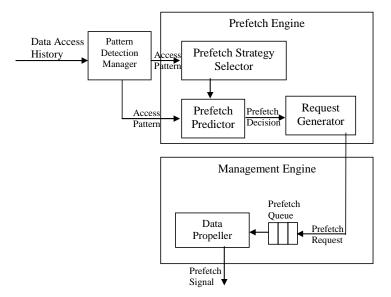

| 3.5 Components of Data Push Server                                          | 28     |

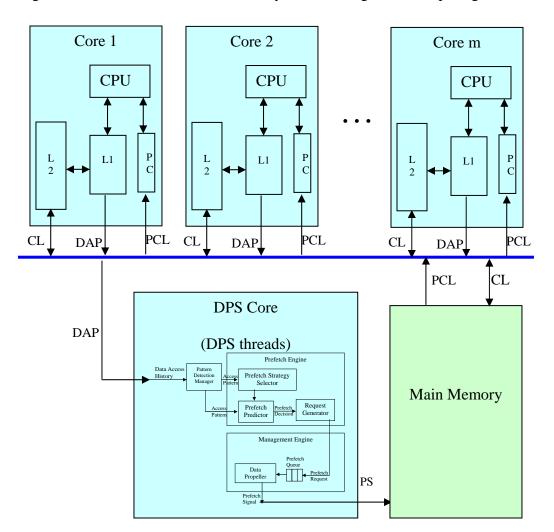

| 3.6 DPS on Multicore processor                                              | 29     |

| 3.7 Data Access History collection for DPS                                  | 31     |

| 3.8 Classification of Data Access Patterns                                  | 33     |

| 3.9 Multi-level Difference Table for variable stride non-contiguous pattern | 36     |

| 3.10 An Example of Multi-level Difference Table                             | 37     |

| 3.11 In time prefetching                                                    | 39     |

| 3.12 Microarchitecture of memory subsystem for DPS                          | 42     |

| 3.13 Modified CPU data request operation                                    | 44     |

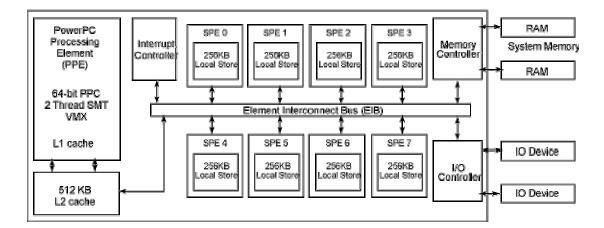

| 3.14 IBM Cell Broadband Engine Architecture                                 | 48     |

| 4.1 Memory-communication cost for a matrix-transpose algorithm              | 55     |

| 4.2 Non-contiguous data access patterns                                     | 58     |

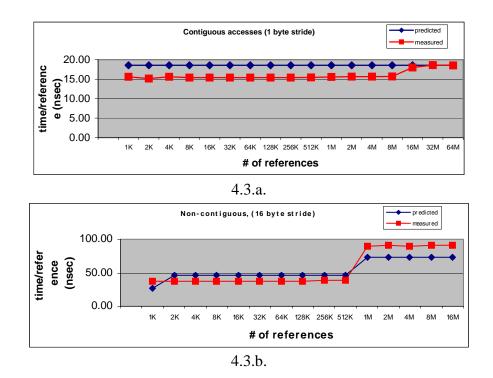

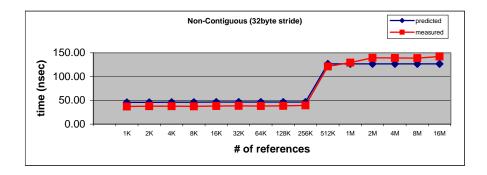

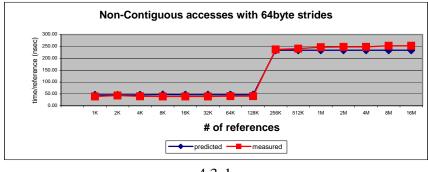

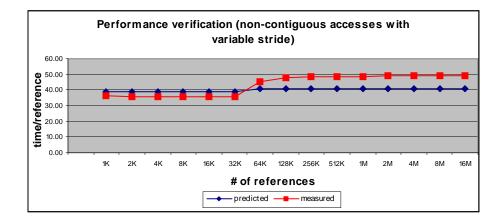

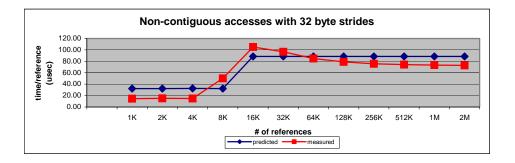

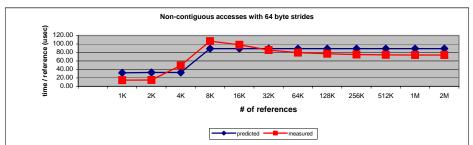

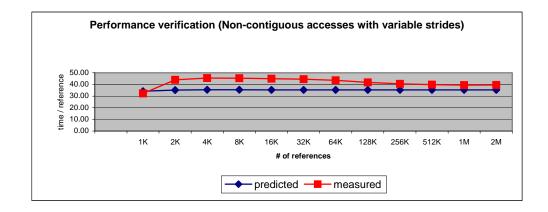

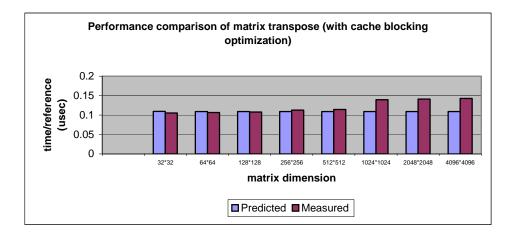

| 4.3 Comparison of measured and predicted memory access cost on UltraSparc   | 67, 68 |

| 4.4 Comparison of measured and predicted memory access cost (2) on UltraSpa | rc 69  |

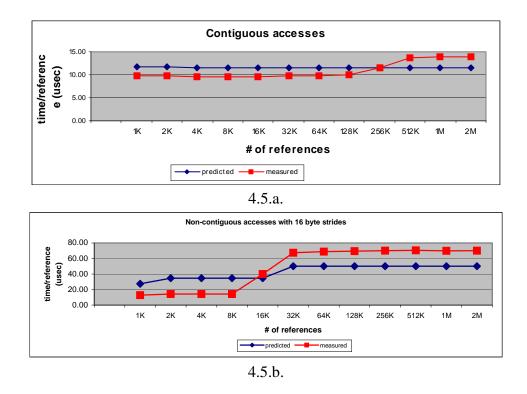

| 4.5 Comparison of measured and predicted memory access cost on P-III (1)    | 70     |

| 4.6 Comparison of measured and predicted memory access cost on P-III (2)  | 71  |

|---------------------------------------------------------------------------|-----|

| 4.7 Comparison of measured and predicted memory access cost on P-III (3)  | 72  |

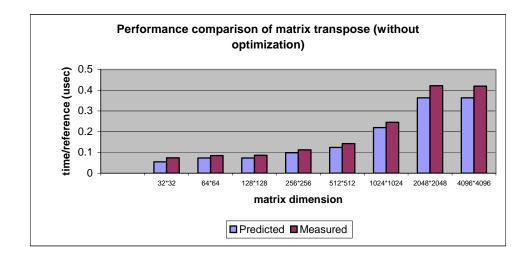

| 4.8 Comparison of measured and predicted cost of unoptimized transpose    |     |

| 4.9 Comparison of measured and predicted cost of optimized transpose      |     |

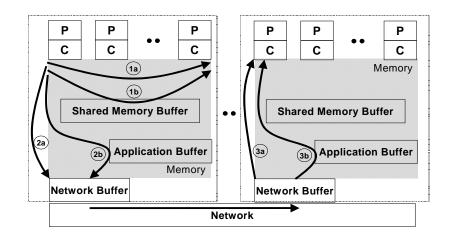

| 5.1 Memory communication within shared memory                             | 78  |

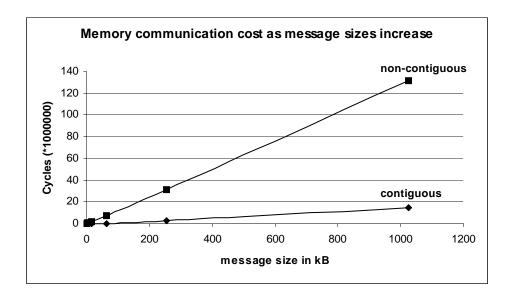

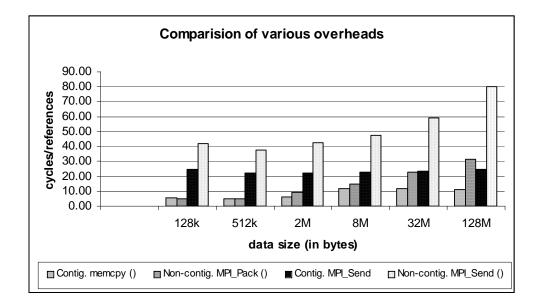

| 5.2 Total cost for sending contiguous and non-contiguous messages         | 83  |

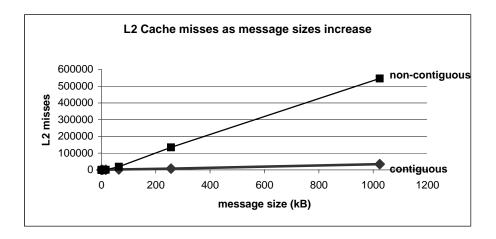

| 5.3 L2 cache misses while sending contiguous and non-contiguous messages  | 84  |

| 5.4 Comparison of cost for various implementations of transpose algorithm | 85  |

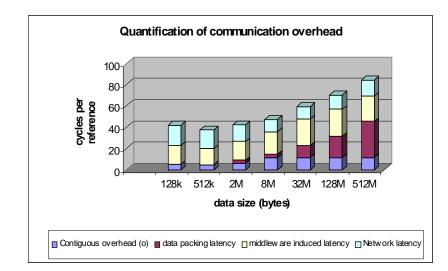

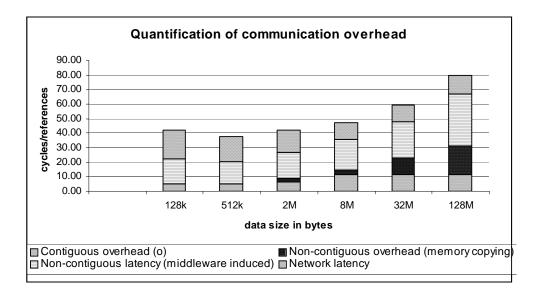

| 5.5 Quantification of communication overhead                              | 87  |

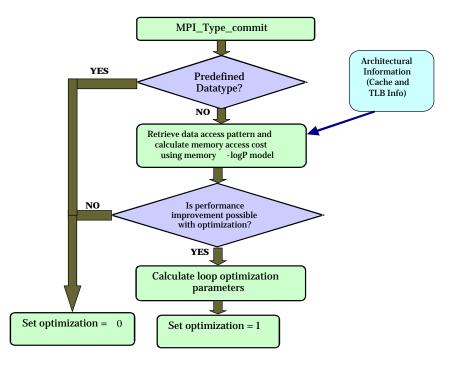

| 5.6 Improving the performance of MPI derived datatypes – Phase I          | 93  |

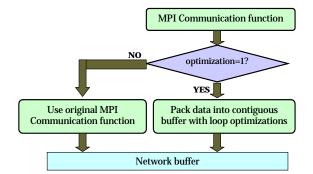

| 5.7 Improving the performance of MPI derived datatypes – Phase II         | 94  |

| 5.8 Current implementation of MPI_Send in MPICH                           | 97  |

| 5.9 Memory-conscious implementation of MPI_Send                           | 98  |

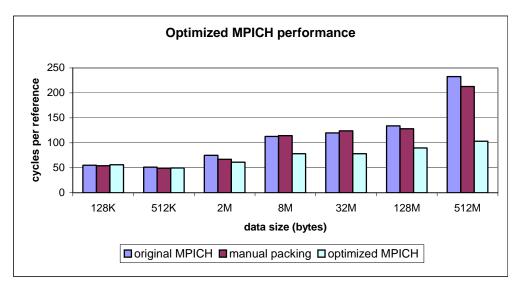

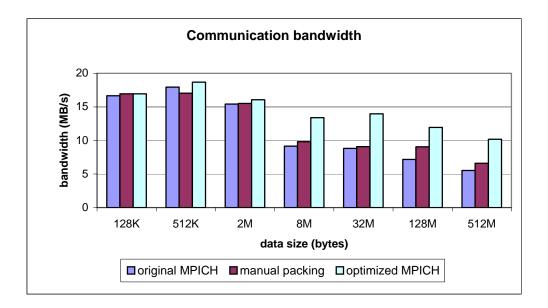

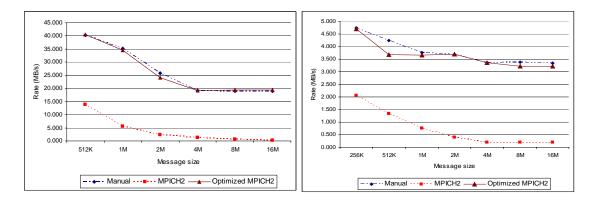

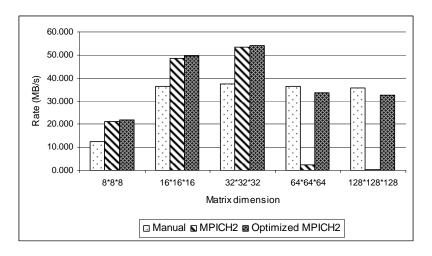

| 5.10 Performance of optimized implementation of derived datatypes         | 102 |

| 5.11 Bandwidth improvement with the optimized implementation              | 102 |

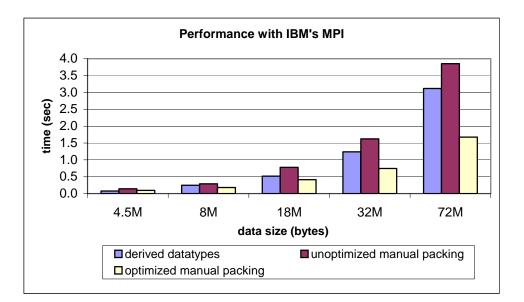

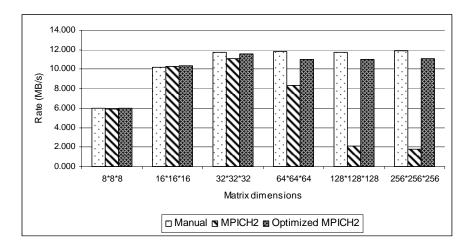

| 5.12 Performance of matrix transpose with IBM's MPI                       | 103 |

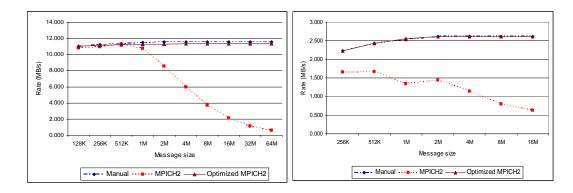

| 5.13 Bandwidth measurements for vector and indexed datatype on jazz       | 106 |

| 5.14 Bandwidth measurements for vector and indexed datatype on sunwulf    | 106 |

| 5.15 Bandwidth measurements for the 3D-cube experiment on jazz            | 107 |

| 5.16 Bandwidth measurements for the 3D-cube experiment on sunwulf         | 107 |

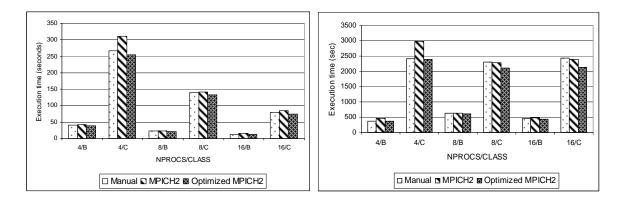

| 5.17 Execution time of the NAS MG benchmark                               | 108 |

| 5.18 Bandwidth measurements for matrix transpose experiment on jazz       | 109 |

| 5.19 Bandwidth measurements for matrix transpose experiment on sunwulf    | 109 |

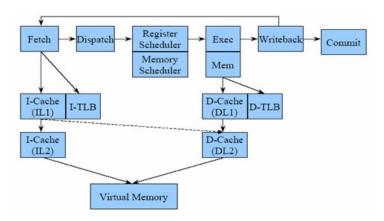

| 6.1 Pipeline for sim-outorder simulator                               | 112 |

|-----------------------------------------------------------------------|-----|

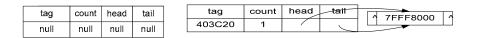

| 6.2 Data Access History (DAH) table                                   | 114 |

| 6.3 3-dimensional nested strided data access                          | 116 |

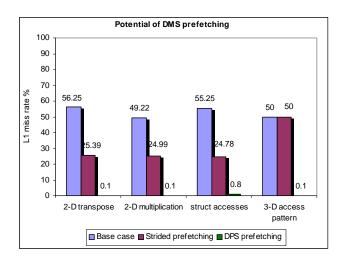

| 6.4 Performance of Kernel benchmarks                                  | 118 |

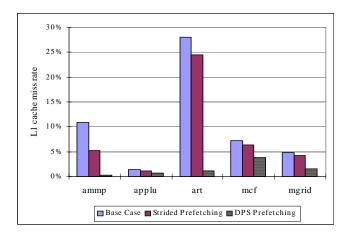

| 6.5 L1 miss rate for SPEC 2000 benchmarks                             | 119 |

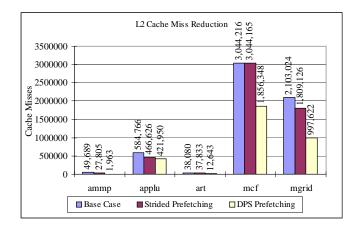

| 6.6 L2 misses for SPEC 2000 benchmarks                                | 120 |

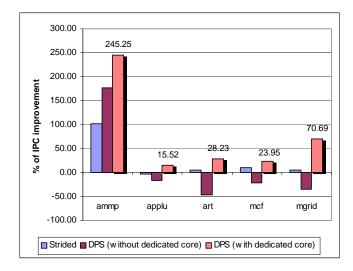

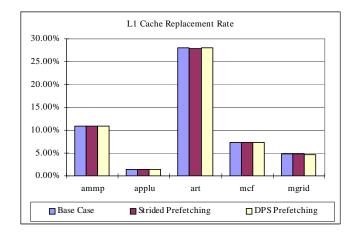

| 6.7 IPC improvement with DPS prefetching                              | 121 |

| 6.8 Effect on replacement rate with DPS prefetching                   | 122 |

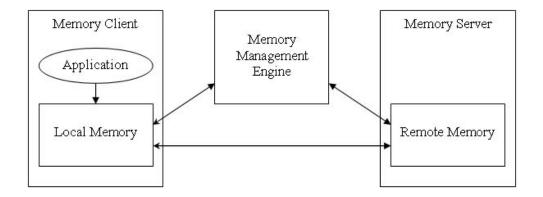

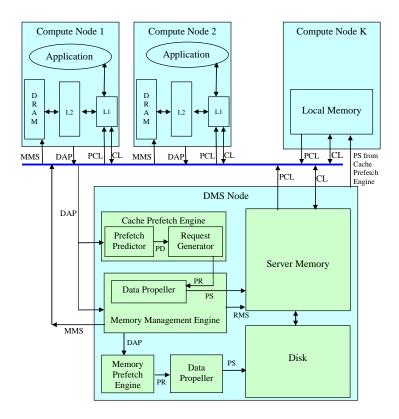

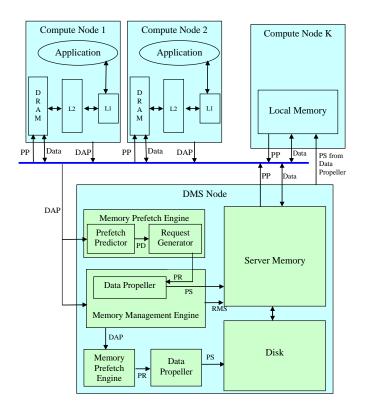

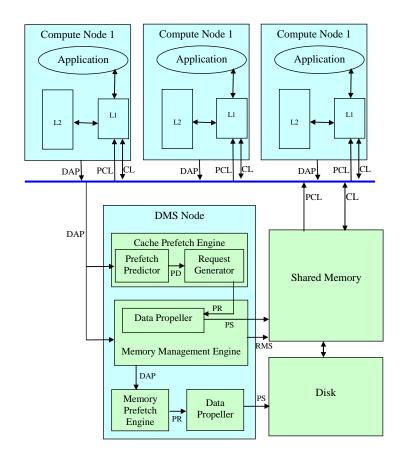

| 7.1 Architecture of Memory Servers                                    | 125 |

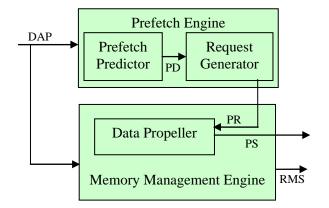

| 7.2 Prefetching Engine                                                | 129 |

| 7.3 Pure Memory Server Model for Clusters                             | 131 |

| 7.4 Hybrid Memory Server Model for Clusters                           | 132 |

| 7.5 Pure Memory Server Model for SMP                                  | 133 |

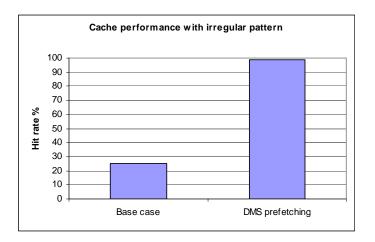

| 7.6 Performance improvement for irregular patterns with pattern hints | 136 |

| 7.7 Directory service of SOA                                          | 137 |

| 7.8 File Access Server                                                | 141 |

| 7.9 Push-based Data Movement                                          | 143 |

| 7.10 Memory performance comparison for file access kernel             | 149 |

# LIST OF SYMBOLS

| Symbol | Definition                              |

|--------|-----------------------------------------|

| HEC    | High-End Computing                      |

| MPI    | Message Passing Interface               |

| SSP    | Sustained System Performance            |

| DSM    | Distributed Shared Memory               |

| SMP    | Shared Memory Parallelism               |

| SMAC   | Simple Memory Access Cost               |

| CBE    | Cell Broadband Engine                   |

| DAH    | Data Access History                     |

| DPS    | Data Push Server                        |

| DPS-P  | Data Push Server for Parallel Computing |

| PFE    | Prefetching Engine                      |

| DAP    | Data Access Pattern                     |

| DPR    | Data Propeller                          |

| PDM    | Pattern Detection Manager               |

| PSS    | Prefetch Strategy Selector              |

| FAS    | File Access Pattern                     |

| DPM    | Dynamic Power Management                |

| DVS    | Dynamic Voltage Scaling                 |

| NIC    | Network Interface Card                  |

| MME    | Memory Management Engine                |

| MLDT   | Multi-level Difference Table            |

| FAS    | File Access Server                      |

| SOA    | Service Oriented Architecture           |

| SPMD   | Single Program, Multiple Data           |

|        |                                         |

#### ABSTRACT

In the past several years, High-End Computing (HEC) has seen enormous growth in peek performance, and development of Peta-flop supercomputer is in the near horizon. Despite these advances, data access delay has been a major reason for poor sustained system performance (SSP) on HEC machines. Multiple levels of memory hierarchy have been incorporated into computer architecture to take advantage of locality among data accesses to reduce the gap between peak and sustained performances. However, many applications lack locality, which make these advances inefficient. Researchers have proposed many optimization methods to improve locality and to prefetch data into these cache memories before CPU demands for it. However, there are limitations in applying these methods. First, locality is application dependent and choosing an efficient combination among all existing tuning methods at runtime remains elusive. Second, the current client-initiated prefetching strategies do not work well for applications with complex, non-contiguous data access patterns.

To bridge the performance gap, we introduce server-based data push architecture. In this architecture, a dedicated server named Data Push Server (DPS) initiates and proactively pushes data closer to the processing units in time. We addressed the issues of monitoring data access history, making spatial and temporal access pattern predictions, architecture modifications to push the predicted data values close to processing cores, and modeling data access cost. We have quantified data access cost from communication and middleware latencies. We present analytical models for memory performance prediction based on data access patterns that are useful to choose effective optimization and prefetching strategies with low overhead. We have applied these models to improve the performance of Message Passing Interface (MPI) derived datatypes. We have studied the server-push architecture by enhancing SimpleScalar simulator with a dedicated processing unit that pushes data for another processor. The simulation results show significant performance gains. Our DPS architecture is extendable to various levels of memory hierarchy, and has a broader impact on high-end computing to improve productivity.

#### CHAPTER 1

#### INTRODUCTION

#### **1.1 DATA ACCESS PERFORMANCE**

High end computing (HEC) is a major strategic tool for science, engineering, and industry. HEC simulations in various areas of science enable to understand the world around us [Abra03, Kusn05]. They study the universe, enabling us to observe the systems that are too small (nanotechnology, biotechnology, DNA analysis etc.), too large (astrophysics, hurricanes, tsunamis, aircraft, atmosphere etc.), and too dangerous (nuclear weapons) for direct experimental observation. HEC machines have emerged with TeraFlops of computing power, and PetaFlop computing is in the near horizon. The current fastest supercomputer IBM BlueGene/L beta-System has 32768 processors, with a peak performance of 367 TeraFlops [Ibmb04]. Even with the existence of these powerful supercomputers, the demand for more powerful supercomputers continues, and many projects are in development to quench computing power thirst.

However, there is a rapidly growing gap between the peak performance of HEC machines and sustained system performance of applications running on these systems [Dhpcs]. While the peak performance of current HEC machines is improving rapidly, the sustained performance of applications on these machines is in the range of meager 10% (see Figure 1.1). Disparity among performance growth of processors, storage, memory, network, and applications has been the cause of this gap. The performance of processor and network interconnect are improving multiple times faster than that of memory and storage. Among these disparities, poor data access performance is a major reason for the divergence gap. Traditionally the performance has been linked to processor speed. The

Figure 1.1. Growing gap between peak and sustained performance Source: HECRTF [Feda04]

capacity and speed of processors doubled every 18 months complying with Moore's Law until 2004, due to the increasing density of transistors within a chip. In contrast, main memory (DRAM) speeds and bandwidth haven't increased enough to catch up with the processor performance. Since 2004, multi-core processor technology is making strides of improvement and the future belongs to these powerful processors. These advances are fueling the performance gap between processing and data access further into new levels. This trend is predicted to continue for the next decade and beyond. The increasing incompatibility between performance of processor and memory has been an obstacle to fully exploit the technological advances and the expected performance from the hardware.

Immense research effort has been spent on reducing the performance gap between processor and memory. Caching is a commonly used method to mask the performance disparity between processing and data access performance. Advanced hierarchical memories that include cache memories at various levels are available to bridge this gap. A cache memory works on the principle of spatial and temporal locality [Smit82], which stores recently accessed cache lines of data. However, there are many applications that lack locality in accessing the memory. These applications spend a major fraction of execution time waiting for data accesses. In other words, cache memories are exploited better if the cached blocks of data are reused extensively before other cache blocks replace them.

Transforming and reordering the memory accesses improve application performance [Mcki96, Kand99, Vudb01]. As loops are the basic blocks, where most of time is spent in HEC applications, various loop optimization techniques have been developed to enhance the memory hierarchy utilization. Loop transformations (loop unrolling, loop fusion, loop interchange, loop reversal and loop tiling) are some of the most effective loop optimizations. Nevertheless, developers have to be aware of these optimization techniques and the location of applying them to improve the performance of applications.

Prefetching is another strategy to mask the data access latency. While caching holds data temporarily, prefetching brings the data to a cache closer to the computing processor before it is requested. Various prefetching strategies have been proposed and developed during the past decade [Chba95, Ctws01, Fupa91, Jogr97, Kasi02]. Based on the data access history, these strategies try to predict future references using the distances (strides) between sequences of accesses. To predict these strides, algorithms are developed ranging from basic constant stride prediction to complex Markov chain predictions. Prefetching instructions can be issued either by a developer or a compiler at software level or by CPU at hardware level. These instructions have to be issued carefully to avoid negative effects of evicting useful cache lines. Accurate prediction and timely issuing of prefetch instructions increase the effectiveness of prefetching.

### **1.2 PROBLEM STATEMENT**

Data access performance can be improved by utilizing cache memory effectively. Accurate and aggressive predictions that help prefetching data in time and automatic reordering of loops can help reduce the CPU stall time in waiting for data access. This is the path to reduce the divergence gap problem of current HEC machines and to improve their productivity.

Although numerous researchers have proposed hardware and software optimization mechanisms to reduce the processor-memory performance gap, memory access is application dependent. Some advanced compilers utilize these optimization techniques at various levels to improve application performance. However, compilers alone are not sufficient to achieve the best possible optimization due to the dynamic behavior of the memory accesses [Bgst03]. Optimizations that are implemented by hand with the knowledge of optimizations, achieve better performance than compiler optimizations. But superior manual optimizations require extensive knowledge of the hardware architecture and also about the data access patterns of application. The developer needs to be aware of efficient optimization techniques to be applied in the right place. Choosing an effective combination of optimizations at runtime among all existing tuning methods is remaining elusive.

Data prefetching at hardware level is a challenging task. Although many strategies exist in literature, their performance varies largely from application to application, and is generally poor on HEC computers. The poor performance of current prefetching technology may be due to different reasons. One noticeable reason is that current prefetching is based on client-initiated prefetching, where the computing processor initiates the prefetching. While letting the computing processor to prefetch the required data seems to be a straightforward solution, client-initiated prefetching has many limitations. For instance, predicting what data to fetch require computing power; aggressive (accurate) prediction algorithms may take computing power away from application and therefore reduce the system performance; the prediction information obtained by the computing processor may get lost in the memory hierarchy; the client does not know where the data is and have to compete with other computing processors for data access, therefore cannot perform in-time prefetching. In addition, in many HEC machines, computing processors have reduced OS implementations. They do not have the means to collect data access information effectively for data access prediction and prefetching. Chip-level multiprocessing puts multiple cores share the same data bus and high-level caches, and puts even more pressure on data access if multicore concurrent processing is conducted.

In recognizing the limitation of client-initiated prefetching, and taking the advantage of the abundant computing power, several new prefetching strategies have been proposed recently on multi-core processors [Alke96, Ctws01, Hafe04, Hugh00, Lwwh02, Lukc01, Roso01, Shpc01]. The main idea of these approaches is to let a helper thread run ahead of the program main thread on a separate core to initiate a load cache misses in a multicore machine. The pre-execution can be conducted on a core close to the program's main thread, which is called *pull-based* pre-execution, or on a core close to the memory, which is called *pull-based* prefetching [Hafe04, Solt02]. The former fits the current multicore chip architecture well. The latter requires special hardware support but is more efficient

in masking data access delay and also realizes the decoupling of data access as suggested by Smith [Smit82].

#### **1.3 OUR APPROACH**

Caching and prefetching techniques enhance data access performance, but they must be applied in HEC application development efficiently. As the time-to-solution of an application includes the time to find a set of optimization parameters, we have to reduce the time to search for optimization parameters at runtime. Prediction of what future data will be used by an application and timing of its usage is important to make prefetching effective. Prefetching incorrect data, either too early or too late has adverse effects on performance. In our research, we introduce strategies to improve caching and prefetching and overall, to bridge the gap between peak performance and sustained system performance of HEC.

We extend the concept of decoupling of computing and data access. We design a data access server system, named Data Push Server (DPS), dedicated to predict data access pattern and to push data closer to computing processors in time. Here the term 'push' also means that, unlike traditional client-initiated prefetching, DPS initiates prefetching. DPS does not conduct any computing or pre-execution. Its whole purpose is to providing data push service and to prefetch based on data access prediction. This further separation of computing and data service has several benefits. First, a dedicated server can adapt to complex prediction algorithms for more aggressive prediction and can push data into multiple computation threads or cores. This is especially beneficial for HEC, where parallel processing is often achieved with the SPMD model [Cull97, Cusg98]. Second,

DPS is flexible to choose strategies dynamically to predict future accesses based on data access history. Instead of looking for a single magical prediction method for all data access patterns, which does not exist, DPS can adaptively choose a prediction method based on the history of accesses and compiler hints. This, again, is very beneficial to HEC where few of the so called "grand challenge applications" often running repeatedly. Third, we use temporal data access information to predict *when* to push data. This avoids costly synchronization needed for pre-execution strategies to initiate prefetching *in time*. DPS can be implemented at various levels of a memory hierarchy.

We have also developed models to classify the data access delay in message passing and to predict that cost based on data access patterns. In message passing, data access delay has become a major portion as the network speeds have improved quite faster compared to memory access performance. To improve the data access cost, we first classified it based on non-contiguity and the size of messages. We then developed a model to predict memory access cost, in order to choose optimization parameters that improve cache utilization. In this process, we used various cache optimization techniques including array padding, cache blocking, software prefetching, and loop unrolling. We applied these models in improving the performance of derived datatypes in the Message Passing Interface implementation MPICH2. MPI derived datatypes allow users to describe noncontiguous memory layout and communicate noncontiguous data with a single communication function. This feature enables an MPI implementation to optimize the transfer of noncontiguous data. Our automatic optimized implementation achieves performance closer to which an advanced developer can achieve by packing/unpacking noncontiguous messages with optimizations. This is a significant performance improvement over original implementation of MPICH2.

#### **1.4 MOTIVATION**

Parallel application developers come from multiple disciplines of scientific research. Their aim is to make their algorithm work more than concerning about improving sustained system performance on HEC machines. This reduces the productivity of these machines and the purpose of building fast supercomputers is defeated. It is necessary to pinpoint the performance bottlenecks and to optimize the performance of parallel codes automatically.

Computer architecture provides various means of improving data access performance, however, it requires locality in data. Many parallel codes access data noncontiguously, where locality does not exist. Instruction level parallelism and memory level parallelism are introduced in superscalar and multicore processors. However, these techniques are beneficial only if data access latency is masked efficiently. Data prefetching has been considered an effective method to mask data access latency. Unfortunately, current data prefetching optimizations are marred by complexity overhead and limiting their effectiveness to a few simple algorithms. There is a need for sophisticated strategies to mask data access latency as well as reducing the divergence gap.

It is the goal of performance optimization techniques to optimize the performance of parallel applications dynamically. These techniques have to avoid any burden on the application developers and utilize numerous structures provided by computer architects. This dissertation focuses on designs and models that attempt to improve data access performance using automatic loop reordering and data prefetching strategies.

### **1.5 THESIS**

Our thesis is as follows. Existing methods of optimizing data access performance require greater support from compilers and developers, which have been proven ineffective. We seek to provide novel analytical models and architecture to effectively and automatically improve data access performance. Our approach is to predict cache optimization parameters analytically in order to reduce the overhead caused by trial-and-error based methods. We have designed an architecture to prefetch data by using aggressive strategies to predict *what* data an application would use in the future and to push that data closer to processor *in time*. These techniques promise applicability in middleware, and are extendable to various levels of memory hierarchy, such as parallel I/O. The objective of our thesis is to automatically improve data access performance in order to achieve superior productivity on high performance computing machines without placing burden on application developers.

## **1.6 OVERVIEW OF THE DISSERTATION**

This dissertation is organized as follows. Chapter 2 provides a literature review of past memory optimization methods in relation to our thesis. We discuss the multitude of approaches of data access optimization methods and attempt to provide arguments for our prediction models and prefetching strategies. Chapter 3 presents our server-based data push architecture. We discuss existing memory subsystem in multicore processor

architecture and present modifications to the microarchitecture of memory subsystem to monitor data access history and push data from DPS. We also discuss data access pattern prediction in spatial and temporal dimensions. In Chapter 4, we provide fundamentals of data access performance models and discuss our prediction models that can be applied for software level data access reordering. In Chapter 5, we show the practical usage of our prediction model in improving the performance of MPI implementation. Chapter 6 provides the simulation results of our server-based data push model. In Chapter 7, we discuss the applications of server-based push model at various levels of memory hierarchy and ways to find energy savings-memory performance tradeoff. Lastly, in Chapter 8, we present overall conclusions, impact of our work in high-end computing field, and the future directions of this work.

#### CHAPTER 2

#### LITERATURE REVIEW

#### 2.1 DATA ACCESS OPTIMIZATION

Poor data access performance has been a growing problem for the last three decades and many researchers attempted to solve the problem. Despite numerous efforts, memory performance is still a bottleneck in high end computing. One major contributing factor to this problem is the growth of processor performance. Processor performance has improved by 52% a year until 2004, and by 25% since [Hepa06]. Memory latencies are high and the number of memory references issued by superscalar processors makes the memory performance even worse. Overlapping the CPU stall time during these memory accesses can be done at hardware level and at software level. At hardware level, providing multiple levels of cache and prefetching data before a CPU requests for it are popular strategies. At software level, modifying applications in order to improve cache utilization and compiler or user inserted prefetching instructions are prominent.

Hardware data prefetching is considered as an effective method of masking CPU stall time. Data prefetching anticipates cache misses and fetches data before processor requests for data. When the anticipation of a future cache miss is correct, CPU stall time that would have been caused due to the cache miss is avoided. The challenge in data prefetching is anticipating future cache misses as well as the time that cache miss occurs. Many researchers have proposed algorithms to predict future references based on the history of cache misses. We discuss existing strategies and their inadequacies in Section 2.2.

Many processor architectures rely on multiple levels of cache memory for exploiting spatial locality and temporal locality of data being accessed. However, this method fails when data accesses are non-contiguous where spatial locality does not hold. Temporal locality does not have effect, when data sizes are very high in addition to non-contiguous data access. Obtaining very high performance is the goal of parallel and distributed programs, where these slow memories prevent in achieving that. The spatial locality of data impacts the performance of parallel algorithms such as the ocean grid solver and Barnes-Hut [Cull97] and other domain decomposition based algorithms. The ocean grid solver exchanges data along horizontal and vertical boundaries. In many domain partition based solutions the boundary data is contiguous and spatial locality is optimal in the cache. When the boundary is non-contiguous (e.g. column boundary in a row-ordered language implementation), the amount of cache misses increase based on the contiguity of the data. The Barnes-Hut application initially operates on adjacent particles with good spatial locality for communication. As the simulation progresses, particles travel through physical space decreasing the spatial locality of communication causing additional cacherelated delays. Many scientific applications have similar noncontiguous patterns. Another example, transmission of a sub-matrix may require a series of non-contiguous accesses incurring more memory latency than contiguous accesses of the same size. Transmissions of data in such cases often utilize the message-passing model, a widely used and accepted parallel programming interface called Message Passing Interface (MPI) [Mpif98]. In Section 2.3, we discuss these performance bottlenecks and related work.

### 2.2 HARDWARE DATA PREFETCHING

Data prefetching is a well studied research area of computer architecture. Traditional hardware data prefetching strategies on single core processors range from simple sequential prefetch strategies to complex Markov prefetching, and to using compiler hints in prefetching and chasing pointers. Sequential strategies [Dads93, Dads95] prefetch next *k* lines of data, while strided strategies [Chba95, Fupa91, Jogr97, Kasi02] predict future strides based on past accesses. With the increasing complexity of these methods, the benefits of prefetching diminish in the traditional client-initiated prefetching. Software-controlled prefetching [Mogu91] gives control to developers or compilers to insert prefetching instructions into programs. Many processors provide support for such prefetching instructions in their instruction set. However, software-controlled prefetching puts burden on developers and compilers, and is less effective in reducing memory stall time on ILP processors due to late prefetches and resource contention [Prra99].

With the emergence of multi-thread support in processors, many thread-based solutions have been proposed to deal with the complexity issue. These methods can be roughly classified into two categories: pre-execution based and prediction based. Pre-execution based methods often use a helper thread to run slices of code ahead of main thread. A small list of various proposals using pre-execution include Luk et al.'s Software controlled pre-execution [Lukc01], Liao et al.'s Software-based speculative precomputation [Lwwh02], Zilles et al.'s Speculative slices [Ziso01], Roth et al.'s Data-driven multithreading [Roso01], Annavaram et al.'s Data graph precomputation [Anpd01], and Hassanein et al.'s data forwarding [Hafe04]. Many of these methods often rely on compiler support to select slices of code to pre-execute and to trigger execution of

that code. Collins et al. [Ctws01] suggest using hardware to select instructions for precomputation. Zhou [Zhou05] and Ganusov et al. [Gabu05] proposed utilizing idle cores of a CMP to speed up single threaded programs. Zhou's *dual-core execution* (DCE) approach uses idle core to construct large, distributed instruction window and Ganusov et al's *future execution* (FE) uses idle core to pre-execute future loop iterations using value prediction. In contrast to pre-execution approaches, our Data Push Server (DPS) system resides on a dedicated data server and adaptively chooses future data prediction strategies aggressively. DPS is designed to serve multiple processing cores simultaneously, where as DCE and FE are tightly coupled to one core. DPS predicts temporal patterns to provide *in-time* prefetching, while pre-execution approaches require synchronization to achieve that.

Prediction based multi-threaded strategies use helper threads to predict future references based on history of past accesses. Solihin et al. [Solt02] propose memory-side prefetching (similar to *push-based* prefetching), where a memory processor is designed to reside within main memory. This memory processor observes history L2 cache misses and predicts future accesses. This scheme uses stride-based and pair-based correlations among past L2 cache misses and pushes predicted data to L2 cache. Our DPS strategy suggests using a dedicated server outside main memory to observe data accesses at L1 cache level and to push predicted data directly either into L1 cache or a separate prefetch cache, which is close to CPU. Based on the observed data accesses, DPS has flexibility to choose multiple prediction strategies and to serve multiple processing cores. DPS also predicts *when* to push data based on temporal pattern of data accesses for in-time prefetching. All these features of DPS make a better system than memory-side

prefetching. Hassanein et al. [Hafe04] also use memory-side prefetching and suggest to forward data to either L1 cache or directly into CPU registers, but their scheme is based on pre-execution. Parts of code are run in a memory processor and the predicted data is sent to L1 cache or registers. In this approach, there is a possibility that the memory processor used to run code being not scalable. If many cores of a CPU are requesting the service from this pre-execution based memory processor, the performance of memory processor degrades. In our DPS approach, we use a server outside memory that is more scalable to serve multiple cores of a processor. Since DPS software can be implemented as a thread, multiple threads can be instantiated, where each thread serves an individual core. This makes prediction of future access patterns more scalable.

Furthermore, DPS is extendable to multi-processor environments such as SMP, where nodes share the same memory. DPS fits well as a memory server in these environments. DPS pushes data from the shared memory to local memory of the compute nodes. Since the server-based push model separates data movement from computing, its impact is fundamental and is beyond the field of HEC. For instance, it can serve as the  $\mu$  proxy between the file server and its clients in a distributed file system to improve scalability; can enhance coherence to provide a single image in a parallel system; and can virtualize storage in a Grid environment. Even in HPC, DPS can be enhanced in language, compiler and scheduling, and can be implemented at system or application level.

#### 2.3 SOFTWARE LEVEL OPTIMIZATIONS

Memory performance of non-contiguous data accesses can be improved by various optimization techniques such as array padding, loop un-rolling, loop transformations, cache blocking etc. Loops are the basic blocks most of the execution time is spent in numerical and scientific applications. Transforming the data access pattern in these is most effective based on the number of iterations each loop runs. *Loop blocking* [W3hp04] minimizes memory system use with multidimensional array elements by completing as many operations as possible on array elements currently in the cache. Loop unrolling [W3hp04] attempts to unroll certain innermost loops, minimizing the number of branches and grouping more instructions together to allow efficient overlapped instruction execution (instruction pipelining). The best candidates for loop unrolling are innermost loops with limited control flow. Loop distribution [W3hp04] moves instructions from one loop into separate, new loops. This can reduce the amount of memory used during one loop so that the remaining memory may fit in the cache. It can also create improved opportunities for loop blocking. Loop fusion combines instructions from two or more adjacent loops that use some of the same memory locations into a single loop. This can avoid the need to load those memory locations into the cache multiple times and improves opportunities for instruction scheduling. Loop interchange changes the nesting order of some or all loops. This can minimize the stride of array element access during loop execution and reduce the number of memory accesses needed. *Outer loop unrolling* unrolls the outer loop inside the inner loop under certain conditions to minimize the number of instructions and memory accesses needed. This also improves opportunities for instruction scheduling and scalar replacement. Data prefetching [Dkkl99] is an effective technique to hide memory access latency. It works by overlapping time to access a memory location with time to compute as well as time to access other memory locations. This inserts prefetching instructions for selected data accesses. We have to be

careful about choosing these accesses to not to prefetch unnecessary data. This technique works well in combination of loop unrolling.

Some advanced compilers provide these optimizations. There had been an immense amount of research to improve the compilers to include all these optimizations [W3nc00, Dkk199]. Despite all these efforts, compilers alone could not be very successful due to their compile time, and architectural constraints. For example, cache performance is sensitive to the block sizes of the data and it depends on cache size, cache line size and associativity very highly. Some of the aggressive optimizations may degrade the performance by transforming already optimized code into sub-optimal code.

As an example, we compare compiler optimization performance with manual optimizations to show that the manual optimization is better than compiler could achieve with the best optimization options. We use matrix-transpose (MT) program in this example, executed on SGI Origin 2000 machine with MIPS 10000 processor. We compiled this program with SGI MIPSpro compiler [W3nc00], which has exclusive library of loop optimizations called LNO. For manual optimizations, we used cache blocking and external array padding for array sizes of 512\*512, 1024\*1024, 2048\*2048, 4096\*4096, and 8192\*8192. Each element is an 8-byte long double. The tested scenarios are:

- a) compilation of MT using –O2 optimizations (default) [mO2]

- b) compilation of MT using -O2 optimizations + cache blocking [mO2cb]

- c) compilation of MT using –Ofast optimizations [mOfast]

- d) compilation of MT using –Ofast optimizations + cache blocking [mOfastcb]

It can be seen from Figure 2.1, that default optimizations are worse than simple manual cache blocking optimization. Using advanced compiler optimizations show improvement over the default options. The last column of manual optimizations in combined with compiler optimizations shows another 100% improvement. This shows the scope for further improvement of performance if the code is developed with these optimizations taken into consideration based on hardware capabilities and software requirements in mind.

Figure 2.1. Comparison of compiler performance with manual optimizations

Finding an effective combination of these manual optimizations requires extensive knowledge of the hardware architecture and data access patterns of application. If a developer is attempting to achieve high performance, he/she needs to be aware of efficient optimization techniques to be applied in the right place. But in practice, it is not common that application developers are aware of all the advances in technology and it is a costly process to "tweak" the code to achieve better performance. For them, it is more important to make their application work correctly and to meet their deadlines of application development. It is performance evaluation researchers' job to worry about finding optimizations, without putting burden on application developers.

To solve the above problem, we need better performance analysis tools and optimization suggestion tools. Several trace-based systems have been designed for performance studies of parallel applications, such as Pablo [Derr99], AIMS [Yasm95]. These systems trace performance data for the whole application and analyze that data to find the bottlenecks. If any part of the code is tuned for improvement, the whole application has to be run to see the performance. The Paradyn system [Mcch95] is a dynamic performance instrumentation and measurement system. This system identifies the performance bottlenecks. But there is no mechanism to show the code tuning approaches that help the user or to apply optimizations automatically in order to improve performance. This needs retrieval of parameters of data access pattern at the bottleneck location and prediction of performance with modified patterns. SCALEA is another tool that does instrumentation, measurement, analysis and visualization. But this still lacks finding the effective combination of tuning methods.

Currently there are few automatic tuning software tools. One of the most popular tools of optimization is Automatically Tuned Linear Algebra Software (ATLAS) [Whal01]. This tool runs subroutines multiple times to obtain the best optimization parameters by a trial and error method. Chung et al. [Chuh04] proposes a method to try several optimization values in the valid range, where previous runs define valid range. This uses machine-learning mechanisms to characterize and prioritize performance issues. This method also needs multiple runs to find a good set of optimizations. A prediction model can remove these multiple runs and be extended to optimize more than just linear algebra subroutines. When the prediction model is simple and fast, it can facilitate to perform the optimization dynamically, at runtime, based on the data access pattern and available memory hierarchy.

Many performance prediction models are available to help programmers in estimating the cost of memory. Copious research effort has been spent in this area to develop accurate cache performance models. But most of these models [Chat00, Sech00, Jaco96] lack generality. They are complex, and are bounded to a few algorithms or data access patterns. Jacob [Jaco96] extracts address traces from the code, which requires execution of the program, and consumes a lot of time if an optimization has to be applied. In our research, we developed a prediction model. We base our prediction model on various access patterns, which are parameterized. This helps in predicting the memory cost with very small complexity and skips the costly process of tracing the references every time data access pattern is changed. Chatterjee et al. [Chat01] studies the exact analysis of cache misses based on the polyhedral model, which is very complex. The Cache Miss Equations model (CME) [Ghos99] is the least costly performance model to our knowledge. However, this model also requires tracing the references to create the reuse vectors and solve cache miss equations. These models are accurate but expensive, and are better choices for static analysis of cache behavior. Our model fits better in choosing the optimization parameters dynamically at runtime than CMEs.

Our model focuses on a wide range of data access patterns with multiple array variables. Most of the other cache analysis models hold good results for a specific algorithm [Chat00, Sech00], but fall short in acquiring generality. In our research, we

aimed to develop models that are simple, practical and reasonably accurate to make performance optimization decisions.

## 2.4 SUMMARY

In this chapter, we presented research work related to data access performance optimization at hardware level and software level. At hardware level, data prefetching is an extensively studied area. Various strategies exist to anticipate future cache misses and data access patterns. At software level, advanced compilers perform loop optimizations; however, they are ineffective with many complex noncontiguous data access patterns. We also discussed memory optimization techniques performed by various frameworks. Despite these efforts, a huge gap between peak performance and sustained performance with numerous applications still exists. Many data prefetching methods need to be more accurate in predicting future reference by using sophisticated and adaptive algorithms. Most of the software level optimization methods are either time consuming or not useful for generic applications. Our research goal at hardware level is to utilize a server and to push data in time to mask the data access latency effectively. At software level, our objective is to provide models that can be used for any application and they are based on data access patterns that cover a wide spectrum of memory accesses. The following chapters provide detailed discussions of our research towards the goal of data access performance improvement. We discuss more related work depending on the context, when we introduce our strategies, models, and implementations.

#### CHAPTER 3

#### SERVER-BASED DATA PUSH ARCHITECTURE

In this chapter, we first introduce the operation of memory hierarchy, memory subsystem of existing processors, and the prefetching support in current general-purpose processors. We then present the design and functionality of our server-based data push architecture. We discuss various technical issues, including how to monitor data access history, what data to prefetch, when to prefetch, how to push data. Finally, we discuss the benefits of implementing DPS on a multicore processor and present a case study of implementing DPS in Cell processor.

#### **3.1 MEMORY SUBSYSTEM**

To bridge the gap between processor and memory performance, modern computer architectures include multiple levels of memory hierarchies. Cache memory and Translation Look-aside Buffer (TLB) are essential parts of this hierarchy. Cache memories are placed either on the die of a processor or outside between CPU and main memory. These are introduced to hold small portions of the contents of main memory that are (believed to be) currently in use. The size as well as the latency increases to access a level of cache as it is placed further from the CPU. It is common to place L1 cache on the die of the processor to make it closer to the CPU. Recent processors (Intel Core Duo architecture [Dowe06] based processors, IBM Power5 and AMD Dual core processors) place L2 cache on the die and extending the cache to another level L3. AMD's processors use large L2 cache instead of L3 cache. In Intel and AMD's dual-core processors, each core has its private L1 cache and shared L2 cache. Cache of virtual memory mappings is stored on Translation Look-aside Buffer (TLB). Processors use virtual addresses to refer to data. These addresses have to be mapped to physical addresses on main memory. Page table contains the full list of such virtual address to physical address mappings and a TLB acts as a cache to store a small number of recently used mapping information. It is becoming common to include more than one level of TLB. IBM's 64-bit PowerPC processors use Segmentation Look-aside Buffer (SLB) to cache the segment information. This replaces segment registers of previous 32-bit architectures of PowerPC.

Figure 3.1. Processing data request by CPU

Figure 3.1 explains how CPU processes a memory request on a traditional single core processor with one level cache and a TLB. We assume that the memory hierarchy follows inclusive property in this subsystem. Baer et al. [Baer88] suggests that it is essential that the contents of higher level cache be a subset of the lower level caches, so that the higher level caches shield the lower level caches from cache coherence interference. Most of current memory hierarchies follow this property. When a memory reference occurs, CPU

initially searches for data in the registers (not shown in the figure). Registers are small in number at the highest level of memory hierarchy and the fastest accessible. If the data is not present in the registers, CPU searches the TLB to find the virtual-to-physical address map. If the mapping entry is found, the next step is to search the L1 cache for the data. If L1 cache does not have the data (which results in an L1 miss), the search continues to the next level cache. If the requested data was never fetched from the main memory, cache misses occur at each level cache. When data is found it is fetched and stored in the L1 cache and returned to the CPU. In the figure, we have shown only one level of cache. Some of the advanced processors search TLB and the L1 cache simultaneously, where cache maintains the virtual address to real address mapping. For the purpose of simple explanation, we assume that the search is sequential. If a virtual-to-physical address mapping is not found in the TLB, the search continues to find the mapping in page table, which resides in main memory. If a requested page has never been fetched into the main memory, the mapping of that page does not exist in the page table, which results in a page fault. In this case, the requested data page is fetched to the main memory and the page table entry is updated. The total cost of accessing memory includes the access time and the miss penalties of these levels in the hierarchy.

The recent revolution of multi-core (dual-core, quad-core and eight-core) processor architectures have increased the computing capacity rapidly. Single core processor speeds have been following the Moore's law, which resulted in 52% improvement in speeds till 2004. From then, Intel, AMD, IBM, Sun has introduced multicore processors, with various designs based on Chip Multi-processing (CMP), thread level parallelism (TLP). In these processors, each chip has more than one core that contains Arithmetic Logical

Figure 3.2. Multicore processor architecture (Intel Core)

Unit (ALU) and one or two levels of cache memory. A typical Intel multicore processor [Dowe06] is shown in Figure 3.2. In this processor, each of two cores has its own L1 Dcache and shared L2 D-cache. The data access operation by CPU cores is similar to the operation shown above (Figure 3.1), except sharing the L2 cache. L1 misses from both cores access shared L2 cache memory. IBM Power5 dual-core processor has similar cache hierarchy with shared L2 and L3 cache memories [Skte05]. Sony/Toshiba/IBM's Cell Broadband Engine (CBE or Cell) is a heterogeneous architecture. Cell processor contains eight symmetric processing elements (SPE core) and one PowerPC processing element (PPE). Each SPE has access to a small local store (local memory) and share a system memory. This multi-core processor revolution has given us an opportunity to introduce new features such as separating the task of data access to improve data access performance.

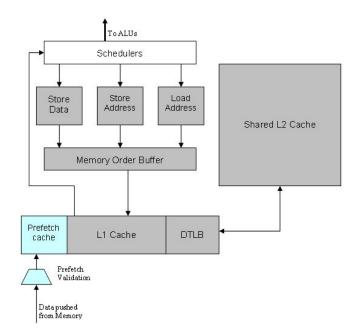

Figure 3.3 shows the detailed memory subsystem of Intel Core architecture [Dowe06]. Schedulers (Reservation Stations) issue various instructions including memory operations. Load and store instructions go to Memory Reorder Buffer (MOB),

where the MOB schedules memory instructions to improve memory level parallelism. If the requested data is in the L1 cache, data is moved to ALUs for processing. If data is not present in L1 cache, a cache miss occurs and propagates to L2 cache and so on. DTLB acts as a cache for memory mapping translations between virtual and physical addresses.

Figure 3.3. Memory Subsystem of Intel Core architecture

Figure 3.4. Instruction Pointer-based prefetcher of Intel Core architecture The Intel Core microarchitecture provides Smart Memory Access (SMA) system [Dowe06], where Instruction Pointer-based (IP) prefetcher is added to L1 level cache (see

Figure 3.4). This prefetcher predicts memory addresses that are going to be used by a program and deliver data just in time. IP prefetcher maintains a Prefetch History Table, where it stores the last address, last stride and last prefetch information. However, the IP prefetcher only "tries" to predict the address of next load, according to a constant stride calculation. When a constant stride is found, Prefetch Generator issues a prefetch request to L1 cache. To avoid contention between regular instructions and prefetch instructions for bandwidth, prefetch requests are given lower priority. If the prefetched data arrives late or predicted references are dropped due to lower priority, the benefit of prefetching is lost.

As mentioned in the previous chapters, the existing prefetching solutions are limited by the power of prefetch generator. They often try to predict only the next load instruction based on constant stride. With the emerging multicore processors with numerous processing cores, not all the cores would be busy with processing. Using the computing power of idle cores or dedicated cores for making data access prefetching decisions is an obvious solution to data access problem. We propose to utilize the power of these computing cores to execute better algorithms to predict complex data access patterns that can adapt the prefetch distance based on latency. The current prefetchers support client initiated *pull-based* prefetching. We aim to use *push-based* prefetching that effectively separates data access from computing as suggested by Smith [Smit82].

#### **3.2 DATA PUSH SERVER ARCHITECTURE**

Data Push Server (DPS) is designed to predict data access patterns of applications and to push the predicted data from main memory to a cache closer to processor. Figure 3.5

Figure 3.5. Components of Data Push Server

shows the structure of DPS. Its three primary components are: pattern detection manager, prefetch engine, and management engine. The pattern detection manager (PDM) collects history of data accesses in spatial and temporal dimensions. Data access information in spatial dimension includes the strides between successive accesses. Information in temporal dimension refers to the time of accesses, either in clock cycles or inter-reference distance. The PDM then classifies patterns of those data accesses. The prefetch engine is responsible to predict future accesses and the timing. It in turn has three subcomponents: prefetch strategy selector, prefetch predictor, and request generator. The *prefetch Strategy* Selector (PSS) adaptively selects an appropriate method to predict future accesses based on the pattern information. The *prefetch predictor* of the prefetch engine decides *what* data to fetch and the *request generator* decides when to push data so that the prefetched data arrives at its destination in time. Here by 'in time', we mean that data is pushed from its source to destination within a window of time before it is required, and where it does not replace other data blocks from cache falsely. By moving data into a cache too early, it may replace data blocks that would be accessed in the near future. Our strategy aims to avoid such negative effects. The Management engine is responsible to issue instructions to push data. The prefetch requests are kept in a prefetch queue and *data propeller* in the management engine issues a signal to push the data to its destination. The source of data in multi-core processor environment is main memory, and the destination is cache memory. Also, when prefetching fails, management engine holds the cache misses as usual.

Figure 3.6 shows a scenario of DPS system running on a computing core, serving

Figure 3.6. DPS on Multicore processor (DAP: Data Access Pattern, PS: Prefetch Signal, CL: Cache Line, PCL: Prefetched Cache Line)

processing cores 1,2, ..., m. We show that each core in a multicore processor environment contains its own L1 and L2 cache memories and shares the memory among other cores. This assumption is true for the future multicore processors announced by Intel, AMD and IBM. The core, on which DPS is running, observes the data access patterns of L1 cache of cores 1 to m, and predicts the future accesses correspondingly. The data (prefetched cache line or PCL) is pushed from the shared main memory to the prefetch cache (PC) of each client core. Data Propeller issues the prefetch signals (PS) to main memory and data is pushed. Regular memory operations related to raw cache misses caused by an application are served by main memory directly. These cache lines are read or written by L2 cache and this data (CL) is transferred main memory and L2 cache. CPU on each core accesses both L1 cache and prefetch cache simultaneously. An L1 cache miss is propagated to lower level L2 cache. A prefetch cache miss is discarded. In the following sections, we discuss the functionality of DPS system components in detail.

#### **3.3 MONITORING DATA ACCESSES**

Monitoring data access history is an important task in order to predict future accesses. There are various methods to obtain an insight into future data accesses by an application, such as user provided hints, compiler hints, and predicting based on history of accesses. If an application developer has prior knowledge of data access patterns in his application, that information can be used. Another method is to utilize compiler provided hints. Existing advanced compilers perform extensive data flow analysis during compilation. Some of this data flow analysis is used to generate software level prefetching instructions [Modk96]. The most common data access monitoring method is to observe the past history to predict sequences of future addresses. Similar to Intel Core architecture shown in Figure 3.4., many existing processors use past history of data accesses. Many researchers [Dads95, Vali00] also consider observing data access history an economical and productive way of predicting future accesses due to minimal hardware modifications.

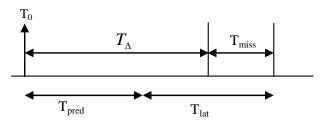

The issue of where to observe the data accesses comes next. Data access history can be observed from cache accesses at L1 cache, cache misses at L1 cache, cache misses at lower level caches. Many previous studies use cache miss history only either at L1 cache or at L2 cache. This can predict future accesses to some extent; however, the accuracy of prediction is low for complex patterns. Moreover, observing cache misses only cannot give an insight into data access times, which is necessary to predict *when* to prefetching. In our technique, DPS observes the data access history at L1 level cache. DPS observes access history of both hits and misses, which helps us in predicting time of future accesses. As shown in Figure 3.7, DPS obtains the history of data accesses at L1 cache to construct comprehensive history, which improves prediction accuracy.

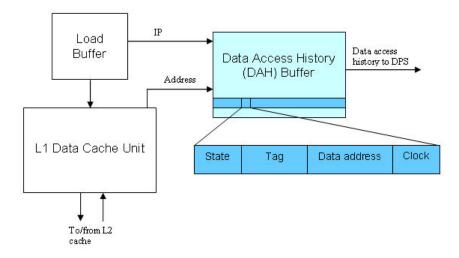

Figure 3.7. Data Access History collection for DPS

The history of data accesses contains state, tag, data address, and clock cycle information. State refers to L1 cache access or L1 miss. Tag field records the instruction address and data address refers to physical address of data requested by the CPU. Clock field records the time of access in cycles. This information is used to predict the temporal pattern of the data accesses and to push data *in time*. As the clock through out the CPU is similar, the core on which DPS is running on has the same clock to synchronize *in time* prefetching.

The data access history is collected temporarily into DAH buffer (Figure 3.7). This buffer is accessed by DPS system. We propose a new instruction called GDAH to retrieve the contents of DAH buffer. GDAH CORE\_ID instruction retrieves data access history from a core identified by CORE\_ID. This instruction provides flexibility of implementing DPS either at hardware level of system level. At system level, DPS can be implemented using helper threads on one of the cores. This is a scalable solution as multiple threads are able to support multiple processing cores.

After collecting history of data accesses, prediction of future accesses is done by the *prefetching engine* of DPS. In research literature, there are many strategies to predict future data references. However, no single strategy accurately predicts all data access patterns. Sequential and strided strategies can predict regular constant and varying strided accesses, while another set of strategies try to chase pointers and data structure traversals [Anpd01, Kcky01, Roms98] that require compiler and user provided hints. Pre-execution based approaches [Gabu05, Hafe04] often use a helper thread to run slices of code to predict future accesses. Complexity of these strategies varies. Using simple strategies cannot capture complex patterns and complex strategies suffer from high overhead in

predicting simple access patterns. An accurate prefetching mechanism should support various prediction strategies and should adapt to data access patterns of an application at runtime.

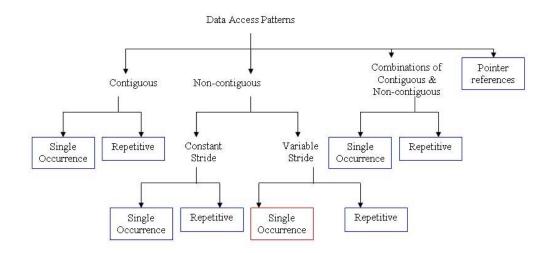

In DPS, the *pattern detection manager* (PDM) detects data access patterns, and the *prefetch strategy selector* chooses an appropriate prediction strategy based on the detected pattern. To detect whether a pattern is formed by simple strides or complex variable strides, the PDM observes the distances (spatial and temporal strides) between consecutive data references. We classify data access references into contiguous, non-contiguous, and combinations of contiguous and non-contiguous patterns. Figure 3.8 shows a classification data access patterns. We divide these patterns further based on repetition of occurrence of each pattern and on variation of strides for non-contiguous patterns. Each pattern is divided into single occurrence, and repetitive patterns. For single occurrence reference pattern, if there is no regularity, future accesses cannot be predicted. Among repetitive patterns, even if there is no regularity in a sequence of accesses, future accesses can be predicted using the past sequence of accesses.

Figure 3.8. Classification of Data Access Patterns

Based on above classification, the PDM characterizes a pattern and passes that information to the *prefetch strategy selector* (PSS). The *prefetch strategy selector* (PSS) chooses a prediction strategy based on initial information regarding a pattern. Many strategies exist to predict future references with similar strides or patterns of strides [Chba95, Fupa91, Kasi02]. Sequential prediction simply adds 1 to current address and brings the next block of data. This is simple and useful to predict contiguous access patterns. Strided prediction uses differences between successive data accesses. If a constant stride exists, future accesses are calculated using that stride. For example, if r is the current data access and d is the constant stride, future accesses are, r+d, r+2\*d, r+3\*d, ..., r+n\*d, where n is the prefetch distance. Stride prediction is useful for constant noncontiguous data access patterns. Using Markov chains [Jogr97] is a more complex strategy, where each data access reference is given some probability of occurrence based on its history. Distance prefetching [Kasi02] uses similar approach, but counts the occurrence of distances between successive references. These two Markov chain based strategies are useful for repetitive patterns.

Table 3.1 gives a summery of prediction strategies that can be used for various data access patterns used in the classification shown above. Sequential, strided and Markov chain based methods predict work well for constant strided patterns, but they are only effective partially when repetitive patterns. Complex variable strided patterns, combinations of contiguous and noncontiguous patterns, and pointer references (marked as XXXX for prediction strategy in the table) need aggressive algorithms in predicting future references accurately. In the next section, we introduce a more complex strategy for predicting future strides.

| Pattern                                                                      | Example of stride                           | Prediction strategy                             |  |  |

|------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------|--|--|

|                                                                              | sequences                                   |                                                 |  |  |

| Contiguous, Single<br>occurrence                                             | 1,2,3,4,5                                   | Sequential prediction                           |  |  |

| Contiguous, repetitive<br>occurrence                                         | 1,2,3,4,5, 1,2,3,4,5                        | Sequential and Markov<br>chain prediction       |  |  |

| Noncontiguous,<br>constant stride, single<br>occurrence                      | 1,5,9,11,                                   | Strided prediction                              |  |  |

| Noncontiguous,<br>constant stride,<br>repetitive occurrence                  | 1,5,9,11,, 1,5,9,11                         | Strided prediction,<br>Markov chain prediction  |  |  |

| Noncontiguous,<br>constant stride,<br>repetitive stride<br>occurrence        | 1,5,9,11,, 2,6,10,12                        | Strided prediction,<br>distance prediction      |  |  |

| Noncontiguous, variable stride, single occurrence                            | 1,3,9,13,                                   | XXXX                                            |  |  |

| Noncontiguous, variable<br>stride, repetitive<br>occurrence                  | 1,3,9,13,, 1,3,9,13                         | Markov chain prediction,<br>distance prediction |  |  |

| Combinations of<br>contiguous and<br>noncontiguous, single<br>occurrence     | 1,2,3,9,15,21, 22, 23, 24,<br>30            | XXXX                                            |  |  |

| Combinations of<br>contiguous and<br>noncontiguous,<br>repetitive occurrence | 1,2,3,9,15,21, 22, 23, 24,<br>30, 1,2, 3, 9 | XXXX                                            |  |  |

| Pointer references                                                           | No specific pattern                         | XXXX                                            |  |  |

Table 3.1. Prediction strategies for data access patterns

## **3.4 PREDICTION OF SPATIAL ACCESS PATTERNS**

As mentioned in the previous section, many strategies exist to predict future references. However, patterns with variable strides and repetitions need more analysis to find regularity among them. With dedicated machine, as computing power is available for prediction, we introduce a new method that predicts regular patterns with constant stride as well as variable stride accesses and repeating patterns. This prediction strategy is based on a finding "*what number comes next*" in the context of number sequences [Cogu96]. This method forms a *difference table* of depth *d*, which we call *multi-level difference table (MLDT)*. Existing strided prefetching [Chba95, Fupa91] and distance prefetching [Kasi02] methods use the distances (strides) between successive page numbers up to one level to find regularity. In MLDT scheme, we extend finding distances for more than one level. Each entry of the *difference table* is the difference between the two entries just above it (in the sense "right entry minus left entry").

| References         | 1 | 4 | 9               | 16              | 25   | 36 | <b>49</b> |

|--------------------|---|---|-----------------|-----------------|------|----|-----------|

| First differences  | 3 | 5 | 7               | 9               | ´ 11 | 13 |           |

| Second differences |   | 2 | $2 \rightarrow$ | $2 \rightarrow$ | 2 ↗→ | 2  |           |

Figure 3.9. Multi-level Difference Table for variable stride non-contiguous pattern

Assume that successive data references are in the order shown in the first line of Figure 3.9. The first differences (d=1) are the strides between the right reference minus the left reference. If these strides are different, differences among these strides are calculated. Second differences (d=2) in Figure 3.9 are equal to a constant value of 2. After a constant difference is found, the next entry of second differences above can be predicted to be the same. As shown in figure 3.9, third entry of second differences is predicted as 2 (predicted entries are marked in bold face and green color font). This is added to the third entry of the first differences, i.e. 7 + 2 = 9. This value is added to the fourth entry of references to find the fifth reference, i.e. 16 + 9 = 25. The future references are predicted (36, 49) in the above example.

In the example above, we have shown finding the address of next data block. We have worked out to find polynomials to predict next  $k^{th}$  reference in a reference sequence.

In figure 3.10, we show a three-level difference table. The references are represented by  $A_i$  (i = 0 to n). The first differences are  $B_i$ , (i = 0 to n-1), second differences are  $C_i$ , (i = 0 to n-2), and third differences are  $D_i$ , (i = 0 to n-3). We present these polynomials up to the depth of three, which can be extended further.

| n                  | 0     | 1     | 2     | 3     | 4                           |                | 5     |       | 6     |

|--------------------|-------|-------|-------|-------|-----------------------------|----------------|-------|-------|-------|

| References         | $A_0$ | $A_1$ | $A_2$ | A A   | <sub>3</sub> A <sub>4</sub> |                | $A_5$ |       | $A_6$ |

| First differences  |       | $B_0$ | $B_1$ | $B_2$ | $B_3$                       | $\mathbf{B}_4$ |       | $B_5$ |       |

| Second differences |       | $C_0$ | $C_1$ | $C_2$ | C <sub>3</sub>              |                | $C_4$ |       |       |

| Third differences  |       |       | $D_0$ | $D_1$ | $D_2$                       | $D_3$          |       |       |       |

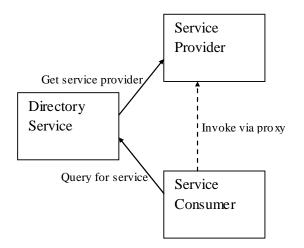

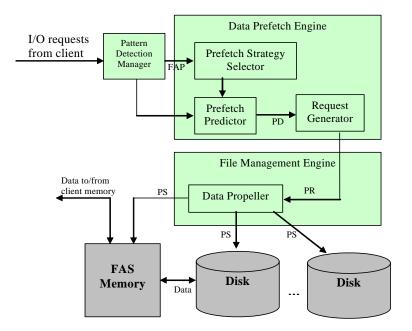

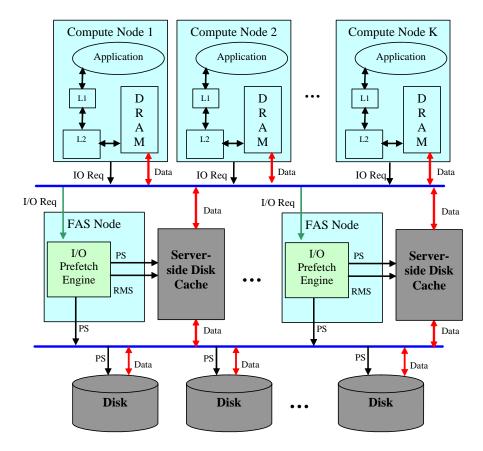

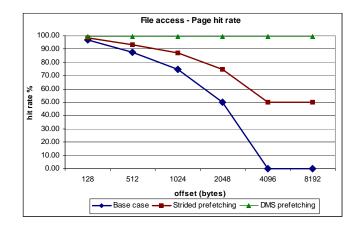

Figure 3.10. An Example of Multi-level Difference Table